我需要对SiC JFET和hard switch 有更多了解

ref:Silvaco Based Electro-Thermal Analysis of 4H-SiC TIV-JFET Structure Under Extremely High Current Density Resistive Switching一篇2016年的文章,用sivalco做的

P+和N+区域的doping都是1E20

SiC横向器件糟糕的原因是:SiC和SiO2界面存在大量缺陷,影响迁移率

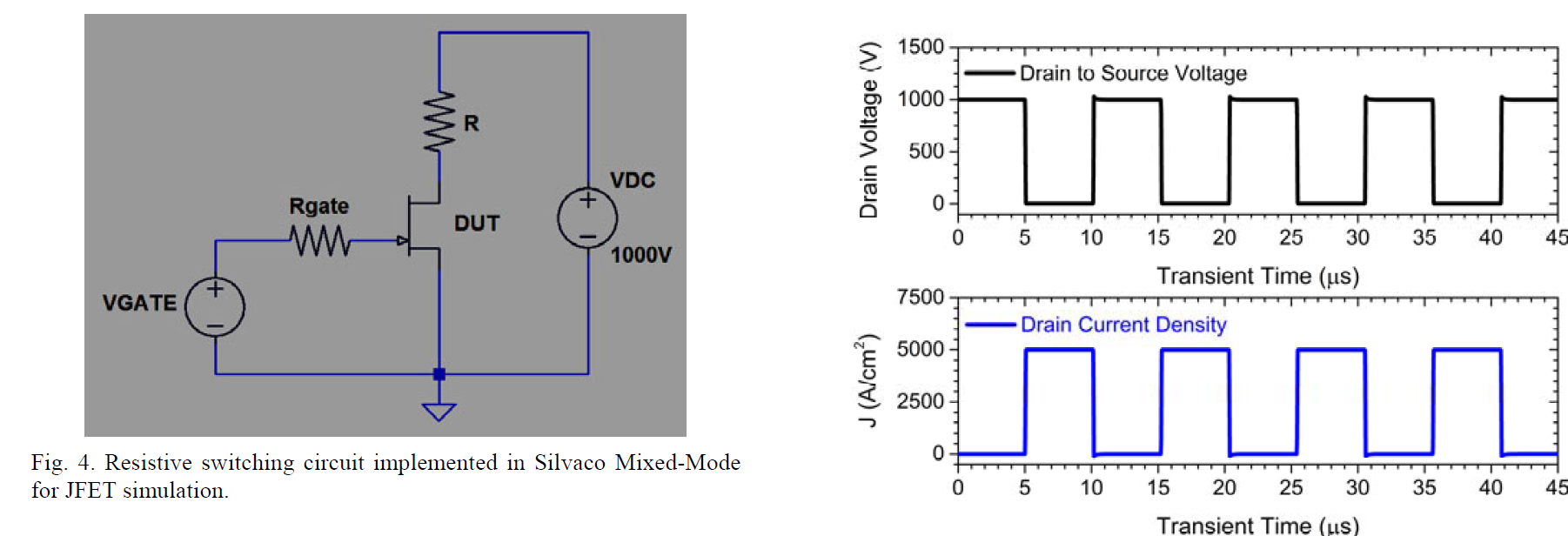

resisitive开关的设置如下

DS上偏压,Gate交流,导通下的电压为2.2V,不知道这个条件和hard switch的条件差多少

on state电流100A/cm2,功耗为0.22KW/cm2,功耗太小了,峰值功耗是20mW/10E-8cm2=2E5/cm2 峰值功耗很高但时间太短了

连续的波形模拟,有点意思

这篇文章没看出什么东西,gate设置没有,边界条件没有

ref:Electrothermal simulations of a thermal sensor integrated with a 4H-SiC JFET

各向异性导热和temperature dependent thermal conductivity

Doping用蒙特卡洛模拟。很合理,它的工况是我需要的,Vgs=0,Vds=15

热点分布和我想的差不多

所以3D仿真的必要性在哪里

ref:Modeling and High Temperature Characterization of SiC-JFET

SiC JFET本身是depletionmode,要得到enhancement,只用把gate和s用一个enhancement连接,这样的效果是

- enhancement未开启时,分压使得gate电压比JFET的S端低,实现关断

- enhancement开启时,Ron很小,JFET的g和s电压接近,器件开启,此时两个器件串联经过电流

- 随着电压增大,enhancement上的分压增加,增加后又进一步“关断”JEFT,然后减小分压

- 最终。S和gate的电压差会被控制在略大于关断电压的范围,这也保护了enhancement

这便是GaN-SiC HyFET的背景。通过上面的分析易知

- Ron和饱和电流由小的决定和(SiC)

- 开启栅压由GaN HEMT决定

- 耗尽区的分布值得仔细思考

- 首先价带导带是连续的,当不同typedoping的材料接触时,会自动形成耗尽区

- 泊松定律决定了单位厚度的某个doping材料能形成的电场增量,因此在电压变化时,spacecharge也会发生变化

- 没有spacecharge(中间的vertical channel)的形成条件是局域等势面,那么从能量的角度上说,spacecharge的单一边界一定是等势的

然后就可以理解vertical channel的存在了,因为尖端聚集效应,偏压的时候这里的电荷密度更大,沿着两段箭头的方向,更薄的材料也能实现需要的压降,vertical channel就产生了

接下来是SiC的电学模型

- space charge的本质是离化dopant形成的固定电荷,那么它们具有1. 单向导电性(因为有电场)2.drift capacitance所以可以被建模成并联的二极管电容

- 然后一个一个端子看就可以了,DS路径很明确

- D往上是drift电阻,随后是RCV描述vertical channel电阻,剩下几坨都是space charge

下一篇ref:Measurement and simulation of short circuit current sharing under parallel connection: SiC MOSFETs and SiC Cascode JFETs

21年这篇也是用silvaco,太好了是silvaco,我们有救了

SC条件指drain和和gate都开启的时候,enhancement mode还没有形成反馈时的低阻态状态,此时电流与电压俱高

欧耶,这个器件中同样有vertical导通区域 电流集中在channel,而热点在channel下方

I versus T